FPGA Editor 工具为设计者提供丰富的FPGA底层编辑功能,主要体现在以下几个方面. (1)在运行自动布局布线器之前,对设计的关键组件和路径进行手动布局布线。 (2)如果自动布局布线器没有完成设计,可以通过于...

”EDA/PLD中的使用FPGA底层编辑器二 EDA/PLD“ 的搜索结果

如图1所示,在【Processes for Source:…】窗口中选择【Implement... 图2 FPGA底层编辑器用户界面 FPGA底层编辑器分为布局窗格、交互式输出窗格、命令输入行、底层元件列表窗格及快捷按钮窗格等。如果在菜单栏选择中

(1)输入文件.NCD:该文件由映射(Map)流程或布局布线(Place&Route)流程生成,使用FPGA Editor可以编辑NCD文件,也可以将最后的结果保存为NCD文件。 (2)输出文件.PCF:物理约束(PCF)文件是映射程序生成...

在执行这些操作前,一定要先保存.NCD和NCF文件。因为任何底层编辑器的操作都会修改这些文件,一旦修改有误,将无法恢复原始设计,造成不必要的损失。... ■使用探点(Probes):在底层编辑器巾叫以增加、删除和保

在布局布线流程中运行底层编辑器与映射(Map)流程中执行的结果是有区别的,其中包含所有布线的详细信息。 图1 FPGA底层编辑器界面 (1)建立一个新的设计或打开一个原有设计,在建立一个新设计之前,需先...

“Tempreture”和“Voltage”是用来设定器件工作条件的约束,这样工具不再使用最坏情况来做分析. 图1 分组中的Miscellaneous约束的Block RAM参数设置 “Feedback”是用来设定DCM或PLL的FPGA外祁反馈延时...

任意波形发生器( Arbit rary Waveform...目前任意波形发生器的研制主要基于DDS 技术, 与传统的频率合成器相比, DDS 具有低成本、低功耗、高分辨率和快速转换时间等优点, 广泛使用在通信、测量与电子仪器领域, 是设

从非常简单的消费类音/视频播放器到在专业制作环境中使用的高度复杂的音视频捕捉、编辑和回放系统,多媒体设备或系统的应用范围非常广泛。人们在实现这类应用系统时会使用特殊应用标准产品(ASSP)、专用数字信号...

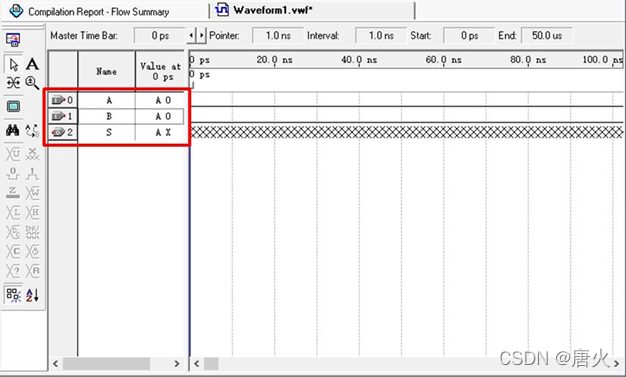

原画图/HDL文本编辑或其他输入方式把电路系统输入到EDA平台中。 编程下载 EDA下载器把适配(结构综合)后生成的编程或配置文件,通过编程器或编程电缆向FPGA或CPLD下载。 仿真验证 对设计结果进行验证,通过预设、...

这款软件的特点在于,它能够将Xilinx开发的一些特定模块嵌入到Simulink的库中,使得用户可以在Simulink环境中进行定点仿真,同时还可以设置定点信号的类型,从而方便用户比较定点仿真与浮点仿真的区别。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA 普遍用于实现数字电路模块,用户可对 FPGA 内部的逻辑模块和 I/O模块重新...

fpga报告

在FPGA开发中,JTAG口更多地被用在对其进行编程、配置、内嵌存储器内容的测试编辑,以及处理器内核系统的软硬件测试和调试。MAX3000A结构中包含五个主要部分,即逻辑阵列块、宏单元、扩展乘积项(共享和并联)、可编程...

EDA与VHDL题库

标签: vhdl

EDA与VHDL题库分享

文章目录第 1 节 开发环境第2节 软件界面第 3 节 第一个上板例程3.1新建工程3.2 代码设计3.2.1 使用官方编辑器3.2.2 使用GVIM编辑器3.2.3 添加文件3.3 编辑设计电路3.4 引脚分配3.5 编程及配置FPGA器件3.6 在线调试...

EDA试题库建设[70%基础题,20%中档题,10%提高题(试题容量:20套试卷,其中每套试题填空题10空(每空2分),选择题10题(每题2分)),简答题4题(每题5分),分析题2题(每题10分),设计题2题(每题10分)。]基础题部分填空题...

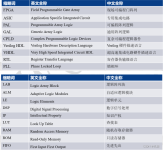

物联网、人工智能、大数据等新兴技术的推动,集成...在这些专业化软件中,EDA(Electronic Design Automation)具有一定的代表性。EDA技术是一种基于芯片的现代电子系统设计方法。它的优势主要集中在能用HDL语言进行输...

EDA课件1_TCH

标签: EDA _TCH

4.布局布线:将.edf文件调入PLD厂家提供的软件中进行布线,即把设计好的逻辑安放到PLD/FPGA内。 5.时序仿真:需要利用在布局布线中获得的精确参数,用仿真软件验证电路的时序。(也叫后仿真) 6.编程下载:确认仿真...

EDA试题库建设[70%基础题,20%中档题,10%提高题(试题容量:20套试卷,其中每套试题填空题10空(每空2分),选择题10题(每题2分)),简答题4题(每题5分),分析题2题(每题10分),设计题2题(每题10分)。]基础题部分填空题(140空)1...

EDA技术概述单元测验-第1章A1、用逻辑门描述一个全加器,是属于那个设计层次:A、晶体管级B、物理级C、门级D、系统级2、module cnt32 ( input clk, output reg[31:0] q ); always @(posedge clk) q = q + 1'b1; ...

EDA主要采用并行工程和“自顶向下”的设计方法,然后从系统设计入手,在顶层进行功能方框图的划分和结构设计,在方框图一级进行仿真、纠错,并用VHDL、Verilog-HDL、ABEL等硬件描述语言对高层次的系统行为进行描述,...

在Modelsim上面进行仿真验证,然后通过SOPC builder设计SOPC系统并且将IP加入进去,结合在niosII IDE里面编写一个三角波软件程序一起烧录在目标硬件环境中去调试通过观察示波器波形完成硬件件验证。通过设计和仿真...

EDA技术与VHDL复习练习题探习题一 >一、填空题TOC \o "1-5" \h \z 1、 PLD的中文含义是:。2、 ASIC的中文含义是: 。3、“与-或”结构的可编程逻辑器件主要由四部分构成:、、和。4、可编程逻辑器件结构图中一般用...

而这种EDA软件的实现目标是:不但要把从输入到上板调试的全过程集成在同一环境中,而且把综合、仿真环境也无遗漏地集成进来。如果把各主流可编程逻辑器件厂家的各系列芯片也兼容进来,软件就具有更好的可移植性和...

VHDL:与Verilog相比,VHDL语法严谨,通过EDA工具自动语法检查,易排除许多设计中的疏忽。 有很好的行为级描述能力和一定的系统及描述能力。 Verilog:代码少,自动类型转换(适合初学者) ,支持版图级,管子集这些...

然后用综合工具将设计转化为具体门电路网表,其对应物理实现可以是PLD或ASIC(专用集成电路)。 2、数字系统的实现方式有哪些?各有什么优缺点? 自顶向下,自底向上; 自顶向下利于早期发现错误,避免设计工作浪费...

推荐文章

- Java---简单易懂的KNN算法_jf.knn-%; 9 &-程序员宅基地

- 最新版ffmpeg 提取视频关键帧_从视频中获取flag-程序员宅基地

- 【ARM Cache 系列文章 11 -- ARM Cache 直接映射 详细介绍】

- Objective-C学习计划

- 【数据结构】最小生成树(Prim算法、Kruskal算法)解析+完整代码

- python访问组策略_python 模块 wmi 远程连接 windows 获取配置信息-程序员宅基地

- html把div做成透明背景,DIV半透明层 CSS来实现网页背景半透明-程序员宅基地

- 关机恶搞小程序

- mnist手写数字分类的python实现_TensorFlow的MNIST手写数字分类问题 基础篇-程序员宅基地

- wxpython窗口跳转_WxPython-用按钮打开一个新窗口-程序员宅基地